# Design and Verification of AES encryption with new approach for S-Box

Bhupendra Badoniya, Ravi Mohan

**Abstract**— Information security has become a very critical aspect of modern computing systems. With the global acceptance of internet, virtually every computer in the world today is connected to every other. While this has created tremendous productivity and unprecedented opportunities in the world we live in, it has also created new risks for the users of these computers<sup>[2]</sup>. The users, businesses and organizations worldwide have to live with a constant threat from hackers and attackers, who use a variety of techniques and tools in order to break into computer systems, steal information, change data and cause havoc<sup>[2]</sup>. The paper work aims at designing and implementing a secure data communication between any two users based on the realization of advanced Symmetric-key Cryptographic algorithm called Advanced Encryption Standard (AES) on an FPGA based processor.

Index Terms— AES (Encryption & Decryption) Algorithm, CPLD (Complex Programmable Logic Design), EDA (Electronic Device Automation), FPGA (Field Programmable Gate Array), ISE (Integrated Simulation Environment), IOB (Input Output Buffer), LUT (Look up table).

### **1** INTRODUCTION

Cryptographic technology is an important way to ensure information security, and is the key to information safety. Among all kinds of cryptographic algorithms, Advanced Encryption Standard Algorithm (AES) is preferred as it offers high security, efficiency, convenient usage, flexibility, and comprehensive performance<sup>[4].</sup>

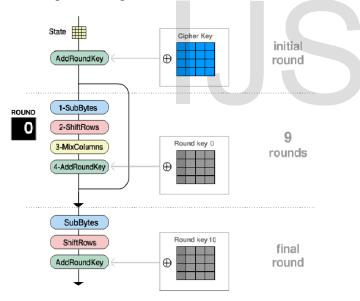

Fig 1. Encryption process Block Diagram

The AES algorithm is a symmetric block cipher that can encrypt, (encipher), and decrypt, (decipher), information. Encryption converts data to an unintelligible form called Cipher-text. Decryption of the cipher-text converts the data back into its original form, which is called plaintext. The AES algorithm is capable of using cryptographic keys of 128, 192 and 256 bits to encrypt and decrypt data in the blocks of bits<sup>[7]</sup>. AES cipher is specified as a number of repetitions of transformation rounds that convert the input plaintext into the final output of ciphertext.

Each round consists of several processing steps, including one that depends on the encryption key. A set of reverse rounds are applied to AES is based on a design principle known as a Substitution permutation network. Unlike its predecessor, DES, AES does not use a Feistel network. AES operates on a 4 x 4 array of bytes called state in a matrix form. The algorithm consists of performing four different simple operations. These operations are: Sub Bytes, Shift Rows, Mix Columns and Add Round Key.

#### 2 DESIGN METHOD

AES operates on a 4x4 array of bytes (referred to as "state"). The algorithm consists of performing 4 different operations<sup>[4]</sup>.

**2.1 SUBBYTES TRANSFORMATION:** is a non-linear byte substitution that operates independently on each byte of the State using a substitution table (S-box)<sup>[1]</sup>.

<sup>•</sup> Bhupendra Badoniya is currently pursuing masters degree program in electronics and communication engineering in RGPV University, India, PH-08359018239. E-mail: bhupendra.badoniya@gmail.com

<sup>•</sup> Ravi Mohan is currently working in Electronics & Communication department in SRIT, Jabalpur RGPV University, India, PH-09406737876. E-mail: ravimohan7677@yahoo.co.in

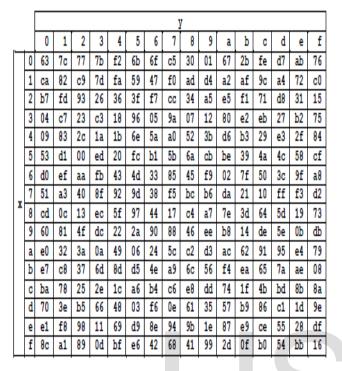

TABLE 1 S-BOX: SUBSTITUTION

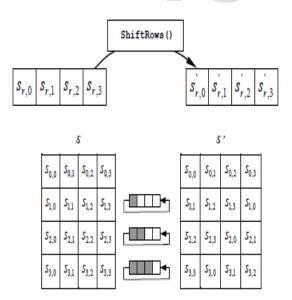

**2.2 SHIFTROWS TRANSFORMATION:** The first row, r = 0, is not shifted. The shift value shift (r, Nb) depends on the row number, r, as follows (recall that Nb = 4):

shift(1,4) =1; shift(2,4) = 2 ; shift(3,4) = 3 Fig 2. ShiftRows ( ) cyclically shifts the last three rows in the state.

**2.3 SHIFTROWS TRANSFORMATION:** The Mix-Columns() transformation operates on the State column-by-column, treating each column as a four-term polynomial. In the

MixColumns step, each column of the state is multiplied with a fixed polynomial a(x).

In the MixColumns step, the four bytes of each column of the state are combined using an invertible linear transformation. The MixColumns function takes four bytes as input and outputs four bytes, where each input byte affects all four output bytes.

Columns are considered with fixed

$$a(x) = \{03\}x^{3} + \{01\}x^{2} + \{01\}x + \{02\}.$$

(1)

Polynomial a(x), given by

Let

$$s'(x) = a(x) \otimes s(x)$$

: (2)

| S <sub>0,c</sub>  |   | 02 | 03 | 01 | 01] | S <sub>0,c</sub> |

|-------------------|---|----|----|----|-----|------------------|

| s' <sub>1,c</sub> | = | 01 | 02 | 03 | 01  | S <sub>1,c</sub> |

| S2,c              |   | 01 | 01 | 02 | 03  | 5 <sub>2,c</sub> |

| S3,c              |   | 03 | 01 | 01 | 02  | S <sub>3,c</sub> |

for 0 = c < Nb MixColumns() operates on the state column-by-column.

**2.4 ADDROUNDKEY TRANSFORMATION:** a Round Key is added to the output of MixColumn operation (state) by a simple bitwise XOR operation. For each round of operation, separate key is generated using Key Expansion.

#### **3 KEY EXPANSION**

Round keys are derived from the cipher key using Rijndael's key schedule. The AES algorithm takes the Cipher Key, K, and performs a Key Expansion routine to generate a key schedule. The Key Expansion generates a total of Nb (Nr + 1) words. The expansion of the input key into the key schedule proceeds as per the functions Rotword(), Subword(), Rcon[i/Nk], Xor operations<sup>[1]</sup>.

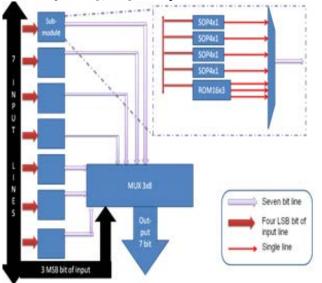

Fig 3. Proposed architecture S8 box

#### 4 TOOL PLATFORMS AND LANGUAGE USED

**4.1 TOOL: XILINX ISE:** It is a software tool produced by Xilinx for synthesis and analysis of HDL designs. Language used: Verilog HDL: Verilog, standardized as1364, is a description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of circuit's the-transfer level<sup>[5]</sup>.

**4.2** PLATFORM USED: FAMILY Vertex4, Device- XC4VLX80, Package-FF1148. Target FPGA is a Vertex FGPA because the same platform is been used by base papers<sup>[5]</sup>.

### **5 SIMULATION AND SYNTHESIZE OF PROPOSED WORK**

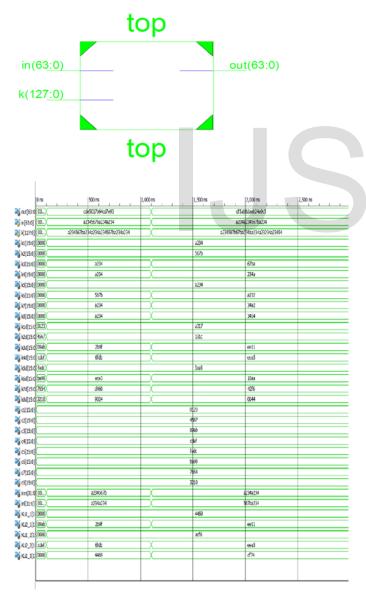

Fig 4. Simulation and RTL schematic of proposed work 6 RESULTS

From the simulation as shown in above slides

Key: A234567ba234a234a234567ba234a234

| Result:-1     |                      |

|---------------|----------------------|

| Output:       | Cde5017b64cd7e93     |

| Input:        | A234567ba234a234     |

| Output^Input: | 6fd15700c6f9dca7     |

| Avalanche:    | 41 bit change/64 bit |

| Result:-2     |                      |

| Output:       | Df5ab6daed24e9c5     |

| Input:        | A234a234567ba234     |

| Output^Input: | 7d6e14eebb5f4bf1     |

| Avalanche:    | 45 bit change/64 bit |

TABLE 2 RESULTS FOR EACH MODULE

# **7 COMPARATIVE RESULTS**

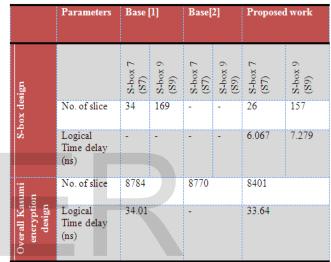

|                 | TABLE 3     COMPARATIVE RESULTS |                 |                 |                     |                     |                              |  |  |  |  |

|-----------------|---------------------------------|-----------------|-----------------|---------------------|---------------------|------------------------------|--|--|--|--|

| Paramete<br>rs  | Design of<br>ET                 | Design of<br>FO | Design of<br>FL | Design of<br>Sbox-7 | Design of<br>Sbox-9 | Complete<br>KASUMI<br>module |  |  |  |  |

| No. of<br>slice | 42<br>9                         | 1379            | 18              | 26                  | 157                 | 8401                         |  |  |  |  |

| No. of<br>LUT's | 78<br>2                         | 2541            | 32              | 52                  | 289                 | 15468                        |  |  |  |  |

| No. of<br>IOB's | 13.<br>04<br>ns                 | 11.216<br>ns    | 4.303<br>ns     | 6.06<br>7 ns        | 7.279<br>ns         | 33.64<br>ns                  |  |  |  |  |

# **8 CONCLUSIONS**

The work is implemented of FPGA which makes proposed

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 ISSN 2229-5518

work a semicustom design as known semicustom design always lack behinds compare to full-custom design in term of Area, speed and power. In future proposed work can be implemented at transistor level (i.e. Full-custom).

#### ACKNOWLEDGMENT

I Bhupendra Badoniya would like to thanks to Prof Ravi Mohan for their valuable support and timely guidelines.

#### REFERENCES

- [1] Dr.R.V.Kshirsagar1, M.V.Vyawahare2, FPGA Implementation of High speed VLSI Architectures for AES Algorithm, 2012 Fifth International Conference on Emerging Trends Engineering and Technology, in 978-0-7695-4884-5/12, 2012 IEEE. DOI 10.1109/ICETET.2012.53

- [2] Shylashree.N1, Nagarjun Bhat2 and V. Shridhar3, FPGA IMPLEMENTATIONS OF ADVANCED ENCRYPTION STANDARD: A SURVEY, International Journal of Advances in Engineering & Technology, May 2012. ISSN: 2231-1963

- [3] Mr. Atul M. Borkar, Dr. R. V. Kshirsagar, Mrs. M. V. Vyawahare, FPGA Implementation of AES Algorithm, 978-1-4244-8679-3/11, 2011 IEEE

- [4] Hassen Mestiri, Noura Benhadjyoussef, Mohsen Machhout and Rached Tourki, An FPGA Implementation of the AES with Fault Detection Countermeasure, CoDIT'13, 978-1-4673-5549-0/13/, 2013 IEEE

- [5] http://www.xilinx.com/support.html

- [6] Wisniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra.

p. 153. ISBN 978-83-7481-293-1

- [7] Thomas Jakobsen and Lars Knudsen. The interpolation attack on block ciphers. In *Fast Software Encryption '97*, volume 1267 of LNCS, pages 28–40. Springer-Verlag, 1997.

- [8] Eli Biham and Adi Shamir. *Differential Cryptanalysis of the Data Encryption Standard*. Springer-Verlag, 1993.

- [9] Mitsuru Matsui. Linear cryptanalysis method for DES cipher. In Advances in Cryptology-Eurocrypt '93, volume 765 of LNCS, pages 386–397. Springer-Verlag, 1993.

# **IJSER**